#### Lab Work Handbook

Version 3.1

E.H.W. van de Logt J.H. Peltenburg J.Z.M. Broeders

#### Lab Work Handbook Programmable Hardware

Versie 3.1

E.H.W. van de Logt J.H. Peltenburg J.Z.M. Broeders

Lab Work Handbook *Programmable Hardware* from Rotterdam University of Applied Sciences is licensed by Creative Commons Attribution-NonCommercial-ShareAlike 3.0 Netherlands license.

### Contents

| In | troduction                                         | 1  |

|----|----------------------------------------------------|----|

| 1  | Purpose and prerequisites                          | 3  |

| 2  | Creating a ModelSim Project                        | 5  |

| 3  | Simulating your design with ModelSim               | 11 |

| 4  | Creating a Quartus project                         | 15 |

| 5  | Assigning signals to physical pins                 | 19 |

| 6  | Place and route the design for FPGA implementation | 23 |

| 7  | Summary                                            | 31 |

| 8  | Tips and further reading                           | 33 |

| Bi | bliography                                         | 35 |

### Introduction

In the modern world of electronics, everything must be fast; the time-to-market must be short and performance must be high. Recently, the PLD (programmable logic device) market has grown tremendously (turnover doubles about every five years<sup>1</sup>) because these devices have become more and more adapt to meet these criteria in many fields of electronics.

FPGAs (field-programmable gate arrays) and other reconfigurable hardware in general are becoming more popular every day. If you have a high-performance application without high power requirements, but you don't have money or time to make an ASIC (application specific integrated circuit), reconfigurable hardware is often a good choice.

HDLs (hardware description languages) capture the functionality of digital schematics in plain text. *In short; a HDL is used to "draw" digital logic with text*. The most widely-used HDLs today are VHDL and Verilog, but there are many others (System C for example). In practise, HDLs are used to design full-scale production ICs, ASICs and especially FPGA configurations.

The power of HDLs is the high level of abstraction. Developing applications with HDLs and letting tools compile and place them in your PLD is faster than drawing schematics by hand. Next to that, the HDL code can often be reused in newer, bigger PLDs and is easily scalable. For example; a well coded 16-bit microprocessor core (captured in HDL) may be changed into a 32-bit microprocessor core by adjusting a few variables only.

The goal of this course is an introduction to VHDL, FPGAs and PLDs in general. The functional designs made by students are implemented into an FPGA that resides on the Altera DE1-SoC development kit.

This document contains the introductory assignment for this course. This first assignment is a step by step introduction to designing and simulating logic with ModelSim and synthesizing and testing it with Quartus.

<sup>&</sup>lt;sup>1</sup> See: https://www.researchandmarkets.com/reports/5398214/fpga-market-by-configuration-lowend-fpga-mid

## 1

### **Purpose and prerequisites**

The purpose of the first introductory assignment is:

- to create a simple functional design with basic logic for a digital system consisting of LEDs and switches;

- to simulate a digital system and thus verify its functionality with ModelSim;

- to introduce you to working with the Quartus Prime software tool;

- to reconfigure an FPGA with a digital schematic.

The perquisites of this assignment are:

- the Terasic DE1-SoC Development Kit is available;

- Intel Quartus Prime Lite edition (version 18.1) software including the has been installed; We use this older version because we want to use the Nios softcore processor in the following up course CSC10;

- ModelSim-Intel FPGA Edition has been installed.

The first thing we will do is create a project in ModelSim to make functional simulations.

## **Creating a ModelSim Project**

**Step 1:** Find and open the link to "ModelSim-Intel FPGA Starter Edition" on your desktop or in the start menu and start ModelSim.

After closing the "Important info" window, it should show the following window:

|                                                   | ile <u>S</u> imu | late A <u>d</u> d Library T <u>o</u> ols Layo <u>u</u> t Boo <u>k</u> marks <u>W</u> indow <u>H</u> elp |          |            |

|---------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------|----------|------------|

| 🖻 • 🗃 🗑 🋸 🍈                                       | X Ph (           | 8 *2 ☆   ② - 🐴 🖺 🗰 🛛 🛛 🕸 🎲 🕍 🐉 【 ColumnLayout AllColumns                                                |          | V          |

| ø <u>⊰</u> - ø <b>⊰ -</b> ø <b>⊰</b> - ø <b>⊰</b> |                  | 0 110 🛐 🗚 🎉 🕴 🛊 🛔 🍰 - 🌨 🏩 📔 Layout NoDesign 💌                                                           |          |            |

| Library                                           |                  | ······                                                                                                  | +        | H 21       |

| Name                                              | Type             | Path                                                                                                    |          |            |

| 220model                                          | Library          | \$MODEL_TECH//altera/vhdl/220model                                                                      |          |            |

| 220model_ver                                      | Library          | \$MODEL_TECH//altera/verilog/220m                                                                       |          |            |

| - altera                                          | Library          | \$MODEL_TECH//altera/vhdl/altera                                                                        |          |            |

| altera_Insim                                      | Library          | \$MODEL_TECH//altera/vhdl/altera_l                                                                      |          |            |

| altera_Insim_ver                                  | Library          | \$MODEL_TECH//altera/verilog/altera                                                                     |          |            |

| ⊣ altera_mf                                       | Library          | \$MODEL_TECH//altera/vhdl/altera_mf                                                                     |          |            |

| altera_mf_ver                                     | Library          | \$MODEL_TECH//altera/verilog/altera                                                                     |          |            |

| altera_ver                                        | Library          | \$MODEL_TECH//altera/verilog/altera                                                                     |          |            |

| arriaii                                           | Library          | \$MODEL_TECH//altera/vhdl/arriaii                                                                       |          |            |

| arriaii_hssi                                      | Library          | \$MODEL_TECH//altera/vhdl/arriaii_hssi                                                                  |          |            |

| arriaii_hssi_ver                                  | Library          | \$MODEL_TECH//altera/verilog/arriaii                                                                    |          |            |

| arriaii_pcie_hip                                  | Library          | \$MODEL_TECH//altera/vhdl/arriaii_p                                                                     |          |            |

| , arriaii_pcie_hip_ver                            | Library          | \$MODEL_TECH//altera/verilog/arriaii                                                                    |          |            |

| arriaii_ver                                       | Library          | \$MODEL_TECH//altera/verilog/arriaii                                                                    |          |            |

| arrialigz                                         | Library          | \$MODEL_TECH//altera/vhdl/arriaiigz                                                                     |          |            |

| arrialigz_hssi                                    | Library          | \$MODEL_TECH//altera/vhdl/arriaiigz                                                                     |          |            |

| arriaiigz_hssi_ver                                | Library          | \$MODEL_TECH//altera/verilog/arriaii                                                                    |          |            |

| arriaiigz_pcie_hip                                | Library          | \$MODEL_TECH//altera/vhdl/arriaiigz                                                                     |          |            |

| arriaiigz pcie hip v                              | Library          | \$MODEL_TECH//altera/verilog/arriaii                                                                    |          |            |

| arriaiigz_ver                                     | Library          | \$MODEL_TECH//altera/verilog/arriaiigz                                                                  |          |            |

| arriav                                            | Library          | \$MODEL_TECH//altera/vhdl/arriav                                                                        |          |            |

| arriav_hssi_ver                                   | Library          | \$MODEL_TECH//altera/verilog/arriav                                                                     |          |            |

| arriav_pcie_hip_ver                               | Library          | \$MODEL_TECH//altera/verilog/arriav                                                                     |          |            |

| arriav_ver                                        | Library          | \$MODEL_TECH//altera/verilog/arriav                                                                     |          |            |

| arriavgz                                          | Library          | \$MODEL_TECH//altera/vhdl/arriavgz                                                                      |          |            |

|                                                   |                  |                                                                                                         |          |            |

| Transcript                                        |                  |                                                                                                         | <u> </u> | <b>⊢</b> ₫ |

| Reading C:/intelFE                                | GA/18.1          | /modelsim_ase/tcl/vsim/pref.tcl                                                                         |          |            |

|                                                   |                  |                                                                                                         |          |            |

| lodelSim>                                         |                  |                                                                                                         |          |            |

|                                                   |                  |                                                                                                         |          |            |

|                                                   |                  |                                                                                                         |          |            |

The library window shows all libraries. Libraries contain components that can be used in simulations. Most of the components in the ModelSim INTEL FPGA Starter edition shown in the list are hardware components inside the physical FPGA that can be used in your designs. There are also some other useful components that can be used for testing. For this course, we will not make use of any of them. Eventually, we will create our own library with our own components (later more on this).

We will first create a new project.

Step 2: Go to File New Project...

You should see the "create project" window.

#### **Step 3:** Fill it in as follows:

| Create Project                       | ×              |

|--------------------------------------|----------------|

| Project Name<br>assignment1          |                |

|                                      |                |

| Project Location                     |                |

| C:/HWP01                             | Browse         |

| Default Library Name                 |                |

| work                                 |                |

| Copy Settings From                   |                |

| modelsim_ase/modelsim.ini            | Browse         |

| Copy Library Mappings C Reference Li | brary Mappings |

| (                                    | OK Cancel      |

#### Step 4: Click OK.

It will probably show a pop-up window that asks if you want to ModelSim to create a directory for your project.

**Step 5:** Let ModelSim create the new directory.

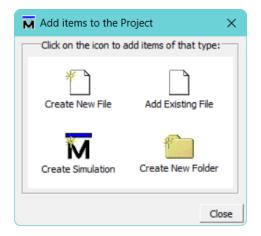

A new window should pop up:

**Step 6:** Click "Create New File."

We will now create our first VHDL file. The extension for VHDL files is .vhd. *The name of the file must be the same of your components name!* Since the component will be named "my\_first\_component" we will name the file my\_first\_component.vhd.

| Create Project File    |                     | ×         |

|------------------------|---------------------|-----------|

| File Name              |                     |           |

| my_first_component.vhd |                     | Browse    |

| Add file as type       | Folder<br>Top Level |           |

|                        |                     | OK Cancel |

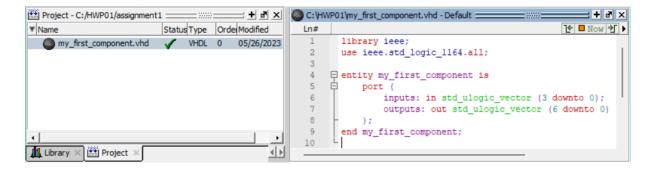

**Step 7:** Click OK and Close to close the "Add items to project" window. Now ModelSim will show the project window:

| ModelSim - INTEL FPGA STARTER EDITION 10.5b |              |              |               |        |                |             |              |                 |                 |        |

|---------------------------------------------|--------------|--------------|---------------|--------|----------------|-------------|--------------|-----------------|-----------------|--------|

| <u>F</u> ile                                | <u>E</u> dit | <u>V</u> iev | v <u>C</u> on | npile  | <u>S</u> imula | te /        | 4 <u>d</u> d | <u>P</u> roject | : T <u>o</u> ol | s Lay  |

|                                             | - 🖻          | 6            | چه خ          | , d    | <u>م</u>       | <u>*</u> ): | ~>           | 🛇 - d           | ₩. ₽            | м      |

| ୍ଥ                                          | • 🐴          | - 🜍          | <b>ii</b> - I | 3]     | * 🍳            | *           |              | - 🚵             | *               | Layout |

| 🛗 Pr                                        | oject -      | C:/HV        | VP01/as       | signme | nt1 🚃          |             |              |                 |                 |        |

| ₹ Nar                                       | ne           |              |               | St     | atusType       | Ore         | dei Mo       | dified          |                 |        |

| N                                           | my_          | first_c      | ompone        | ?      | VHDL           | 0           | 05/          | 12/2023         | 3 06:11:        | 21     |

| <b>i i ii</b>                               | brary        | × 🛗          | Projec        | t ×    |                |             |              |                 |                 |        |

We can see our VHDL file included in the project. The status of the file, which is a question mark, means that the file is not compiled yet. We will do this later.

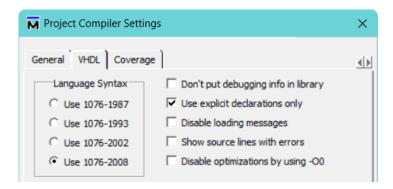

We will use the latest (2008) version of the VHDL standard.

**Step 9:** Double-click on the file to edit it. Add the following lines to the file:

```

library ieee;

use ieee.std_logic_1164.all;

entity my_first_component is

port (

inputs: in std_ulogic_vector(3 downto 0);

```

## outputs: out std\_ulogic\_vector(6 downto 0) ); end my\_first\_component;

The first two lines define the standard libraries that contain many different functions and data types in VHDL we want to use for this (and probably any other) project.

The **entity** part defines the interface of our functional block. The **port** part inside the **entity** defines which ports we want to see at the interface of our functional block. It does not define the implementation of the functionality of the block itself. This is done in the **architecture** section.

This concept, the difference between and separation of the *interface* and the *implementation* of a (sub)system, is the key to system engineering in any field.

in std\_ulogic\_vector(3 downto 0) defines an input port (high impedance). std\_ulogic is a basic digital connection. A vector makes it a group or bus of inputs. 3 downto 0 tells us that the bus is four bits wide. This is the VHDL notation for a bus. Note that we have written it in MSB-first style (Most Significant Bit first).

**Step 10:** Save the file.

We have now declared the interface of your component. What is missing is how it should behave. This is done in the architecture. However, only declaring the interface is enough to compile our component.

**Step 11:** Right click on the file and select Compile Selected

You should now see the following:

Note that the status of the component has also changed to a green  $\checkmark$ . This means it compiled successfully. If it didn't compile successfully it would show a red  $\checkmark$ . Even though we compiled the component, we cannot simulate it, because we have not declared how it should behave. This can be done by adding the **architecture** section to the code.

**Step 12:** Add the following lines to the file:

```

architecture implementation of my_first_component is

begin

outputs(0) <= inputs(0);

outputs(1) <= inputs(1);

outputs(2) <= inputs(0) or inputs(1);

outputs(3) <= inputs(0) and inputs(1);</pre>

```

```

outputs(4) <= inputs(0) and inputs(1) and inputs(2) and ↔

inputs(3);

outputs(5) <= inputs(0) or inputs(1) or inputs(2) or inputs(3);

outputs(6) <= not(inputs(0) or inputs(1) or inputs(2) or ↔

inputs(3));

end implementation;</pre>

```

The outputs are now some combinational function of the inputs.

**Step 13:** Fill in the truth table for this function, shown below.

| inputs | outputs |

|--------|---------|

| 0000   | 1000000 |

| 0001   | 0100101 |

| 0010   | 0100110 |

| 0011   | 0101111 |

| 0100   |         |

| 0101   |         |

| 0110   |         |

| 0111   |         |

| 1000   |         |

| 1001   |         |

| 1010   |         |

| 1011   |         |

| 1100   |         |

| 1101   |         |

| 1110   |         |

| 1111   |         |

We will now verify these results by simulating our little design.

### Simulating your design with ModelSim

**Step 14:** In the ModelSim menu, select Simulate Start Simulation....

After opening up the "work" library, you should see the following dialog:

| * Name         | Type    | Path                               | 1  |

|----------------|---------|------------------------------------|----|

| +-             | Library | work                               | 12 |

| + 220model     | Library | \$MODEL_TECH//altera/vhdl/220model |    |

| + 220model_ver | Library | \$MODEL_TECH//altera/verilog/220m  |    |

| + dlera        | Library | \$MODEL_TECH//altera/vhdl/altera   |    |

| → altera_Insim | Library | \$MODEL_TECH//altera/vhdl/altera_l |    |

| Design Unit(s) |         | Resolution                         |    |

| 2 17           |         | default                            |    |

When we created the project, we called our default library "work". This library now appears with all our compiled components in the dialog. Expand the library "work", and you can see "my\_first\_component" appearing there. You may even expand the component in the list to see which implementations are available. In our case, we have only one implementation which is called "implementation".

| M Start Simulation        |             |                                    | ×      |

|---------------------------|-------------|------------------------------------|--------|

| Design VHDL Verilog Libra | aries SDF   | Others                             | <.     |

| ▼ Name                    | Туре        | Path                               |        |

| - 1 work                  | Library     | work                               |        |

| E my_first_component      | Entity      | C:/HWP01/my_first_component.vhd    |        |

| A implementation          | Architectur | e                                  |        |

| ⊥ 220model                | Library     | \$MODEL_TECH//altera/vhdl/220model |        |

|                           | Library     | \$MODEL_TECH//altera/verilog/220m  | -      |

| Design Unit(s)            |             | Resolution                         |        |

|                           |             | OK                                 | Cancel |

**Step 15:** Select "my\_first\_component" and click OK to start the simulation.

You should now see the following window:

| ModelSim - INTEL FPGA STARTER EDI                                             | FION 10.5b                                                                      |                                    | – o x                    |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------|--------------------------|

| File Edit View Compile Simulate                                               | A <u>d</u> d T <u>r</u> anscript T <u>o</u> ols Layo <u>u</u> t Boo <u>k</u> ma | rks <u>W</u> indow <u>H</u> elp    |                          |

|                                                                               | 🔍   💿 - 🗛 🚉 🗰 🙀                                                                 |                                    |                          |

| 🔄 🚹 🦛 🖦   📑 🛛 100 ps 🜩 [                                                      | El El El 🕅 🌰   🛄 🗐 🖑 🛛 Colum                                                    | nLayout AllColumns                 |                          |

| X X 🖹 🐐 🛛 I o 10 🗊                                                            | all 🎉 🗍 🦓 • 🐴 • 🤣 🕋 • 🤹 🗍 🏌                                                     | 砱 🛊 🕴 📩 + 🏤 🏦 📙 Layou              | t Simulate 🗨             |

|                                                                               | 💫 Objects 👬 🗾 📩                                                                 | N y_first_component.vhd (/my_first |                          |

| Instance     Design unit                                                      | ▼Name Value 💽 Now 🏞 🕨                                                           | Ln#                                | 1 🗖 Now 🔁 🕨              |

| my_first_comp my_first_com                                                    | 💽 🍫 inputs UUUU Signal In                                                       | <pre>1 library ieee;</pre>         |                          |

| line13 my_first_com                                                           | 王 🛧 outputs UUUUUUU Signal Out                                                  | 2 use ieee.std_lo                  | ogic_1164.all;           |

| line14my_first_com                                                            |                                                                                 | 3<br>4 Elentity my first           |                          |

| line_15 my_first_com                                                          |                                                                                 | 4 entity my_first<br>5 port (      | _component 18            |

| line16 my_first_com                                                           |                                                                                 | T                                  | in std ulogic vector     |

| — line17 my_first_com     — line18 my_first_com                               |                                                                                 | anpace.                            | s: out std ulogic vector |

| line_19 my_first_com                                                          |                                                                                 | 8 - );                             | . out sta_arogre_vecte   |

| standard standard                                                             | · · · · ·                                                                       | 9 end my first o                   | component;               |

| textio textio                                                                 | 🌼 Processes (Active) 🚃 📰 🛨 🗗 🗙                                                  | 10                                 |                          |

| std_logic_1164 std_logic_1164                                                 | Name Type (filtered) State                                                      | 11 architecture i                  | mplementation of my i    |

|                                                                               | line 19 VHDL Process Activ                                                      | 12 🛱 begin                         |                          |

|                                                                               | line 18 VHDL Process Read                                                       | 13 outputs (0)                     | <= inputs(0);            |

|                                                                               | line 17 VHDL Process Read                                                       | 14 outputs (1)                     | <= inputs(1);            |

|                                                                               | line 16 VHDL Process Read                                                       | 15 outputs (2)                     | <= inputs(0) or ir       |

|                                                                               | line 15 VHDL Process Read                                                       | 16 outputs (3)                     | <= inputs(0) and ing     |

|                                                                               | line 14 VHDL Process Read                                                       | 17 outputs (4)                     | <= inputs(0) and inp     |

| <b>▲</b>                                                                      | line_13 VHDL Process Read                                                       | 18 outputs (5)                     | <= inputs(0) or inp      |

| 👖 Library 🛛 🛗 Project 🗡 🛺 sim 🔹 🕨                                             |                                                                                 |                                    |                          |

|                                                                               |                                                                                 |                                    |                          |

| 📮 Transcript 🦾                                                                |                                                                                 |                                    |                          |

| ModelSim> vsim -gui work.my_first_                                            |                                                                                 |                                    | <b></b>                  |

| <pre># vsim -gui work.my_first_compor</pre>                                   |                                                                                 |                                    |                          |

| # Start time: 12:06:32 on May 13                                              | 3,2023                                                                          |                                    |                          |

| # Loading std.standard                                                        |                                                                                 |                                    |                          |

| <pre># Loading std.textio(body) # Loading ieee.std_logic_ll64(body)</pre>     | odu)                                                                            |                                    |                          |

| <pre># Loading leee.std_logic_lie4(b) # Loading work.my_first_component</pre> |                                                                                 |                                    |                          |

| VSIM 2>]                                                                      |                                                                                 |                                    | -                        |

|                                                                               | Project : assignment1                                                           | ow: 0 ps_Delta: 0                  | sim:/my_first_component  |

|                                                                               | Project assignmenti N                                                           | uni upa Della. U                   | jaint/my_mst_component   |

This is the simulation setup of ModelSim. In the "Instance" window we can see all components and their underlying architectures and processes from which we can select objects to include in the simulation. All objects that can be included are shown in the "Objects" window.

We can clearly see our signals inputs and outputs here.

Now, if we want to simulate our design with all the signals that are in it do the following:

Step 16: Right click in the "Objects" window.

Signals in Design.

All signals are now added to the "Wave" window. We can now see our signals in the wave window:

| 👥 Wave - Default 🕂 🗗 🗙 |               |              |              |        |       |     |  |  |

|------------------------|---------------|--------------|--------------|--------|-------|-----|--|--|

| 💫 🗸                    |               | Msgs         |              |        |       |     |  |  |

| /my_first_co           |               |              |              |        |       | •   |  |  |

| AL 📰 🛞                 | Now           | 0.0000000 ms | 000 ms       | 0.0000 | 02 ms |     |  |  |

| ê 🖉 🤤                  | Cursor 1      | 0.0000000 ms | 0.0000000 ms |        |       |     |  |  |

| 4                      | Þ             | ∢ ►          | •            |        | ► I   |     |  |  |

| M my_first_compone     | nt.vhd 🗙 📰 Wa | ve ×         |              |        |       | < > |  |  |

**Step 18:** Open the force window on the signal **inputs**.

| Force Selected Signal X  |            |           |  |  |  |  |  |

|--------------------------|------------|-----------|--|--|--|--|--|

| Signal Name: sim:/my_fir | st_compone | nt/inputs |  |  |  |  |  |

| Value: 0000              |            |           |  |  |  |  |  |

| • Freeze C Drive         | C Deposit  |           |  |  |  |  |  |

| Delay For: 0             |            |           |  |  |  |  |  |

| Cancel After:            |            |           |  |  |  |  |  |

|                          | OK         | Cancel    |  |  |  |  |  |

The value here is shown as UUUU. Remember that the inputs signal is a vector of four values. The inputs are currently all unknown (U).

Step 19: Change the value to 0000.

This means that **input(0**) will get the value 0. **input(1**) will get the value 0 as well, and so forth.

**Step 20:** Click OK to apply the changes.

You will not see any changes right away in the wave window, but that is because the simulation hasn't started yet.

Step 21: To run the simulation for 100 time steps, go to menu. Click Simulate Run Run 100.

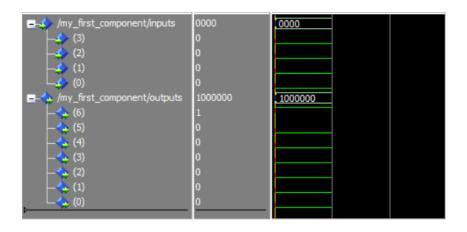

The Wave window should now show (to enlarge hold the Ctrl button down while scrolling with the mouse):

| 📕 Wave - Default + 🗗 >          |              |              |  |  |  |  |  |  |

|---------------------------------|--------------|--------------|--|--|--|--|--|--|

| <b>€</b> 1 •                    | Msgs         |              |  |  |  |  |  |  |

| + /my_first_component/inputs    | 0000         | 0000         |  |  |  |  |  |  |

| /my_first_component/outputs     | 1000000      | 1000000      |  |  |  |  |  |  |

| A I I O Now                     | 0.0000001 ms | 1000 ms      |  |  |  |  |  |  |

| Cursor 1                        | 0.0000000 ms | 0.0000000 ms |  |  |  |  |  |  |

| ₹ F                             | . →          |              |  |  |  |  |  |  |

| M my_first_component.vhd 🗶 🔢 Wa | ve ×         | < >          |  |  |  |  |  |  |

You can also expand the signals that are vectors to show their individual elements. This should look like this:

Verify that the outputs have the correct values (corresponding to your code).

**Step 22:** Now force the inputs to 0001 and repeat until you have tested all possible inputs (assume the values of each individual input can only be 0 or 1.

Take a screenshot of the wave window which shows all possible input values and the associated output values. Compare the output values with the expected values given in the truth table you filled in at step 13.

Verifying your design by forcing all possible input combinations one by one and comparing the simulation results from the wave window with the intended behavior in the truth table is a time-consuming and error-prone job. During this course you will learn a better way to verify your design by using a so called "testbench".

If you are not sure your design works properly, call your instructor to verify your results.

## 4

## **Creating a Quartus project**

Now the design is ready to be exported to Quartus, so we may continue to implement it with the FPGA.

- Start "Quartus (Quartus Prime 18.1)" from the desktop or from the start menu.

- Start the "New Project Wizard".

- Skip the introduction of the Wizard.

- In the "Directory, Name, etc." page of the wizard, select the same directory as your ModelSim project as the working directory.

- Name the project "assignment1" as well.

- The top-level entity is our component called "my\_first\_component". If you decide to add a different top level later, it is easy to change after you've completed the wizard.

Eventually, the current page should look as follows:

| 🕥 New Project Wizard                                                                                                                                        | × |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Directory, Name, Top-Level Entity                                                                                                                           |   |

| What is the working directory for this project?                                                                                                             |   |

| C:/HWP01                                                                                                                                                    |   |

| What is the name of this project?                                                                                                                           |   |

| Assignment1                                                                                                                                                 |   |

| What is the name of the top-level design entity for this project? This name is<br>case sensitive and must exactly match the entity name in the design file. |   |

| my_first_component                                                                                                                                          |   |

| Use Existing Project Settings                                                                                                                               |   |

#### Step 23: Click Next.

Step 24: Set Project Type to "Empty Project" and click Next.

On the next page (Add Files), since we've already created a VHDL file, we can easily include it in the project by clicking Add All. The page should now look like this:

| 🕞 New Project Wizard                                               |                                  |            |                  |       |                  | × |

|--------------------------------------------------------------------|----------------------------------|------------|------------------|-------|------------------|---|

| Add Files                                                          |                                  |            |                  |       |                  |   |

| Select the design files you wa<br>design files in the project dire |                                  |            | oject. Click Add | All t | o add all        |   |

| Note: you can always add des                                       | ign files to t                   | he project | t later.         |       |                  | _ |

| <u>F</u> ile name:                                                 |                                  |            |                  |       | <u>A</u> dd      |   |

| •                                                                  |                                  |            |                  | ×     | Add A <u>l</u> l |   |

| File Name                                                          | ne Type Library Design Entry/Syn |            |                  |       |                  |   |

| my_first_component.vhd                                             | VHDL File                        |            |                  |       | <u>U</u> p       |   |

#### Step 25: Click Next.

In the Family and Device Settings page, we have to select which FPGA we're using. Our programming tools are well capable of selecting the proper device automatically (this is done through the JTAG chain), but let us select the right FPGA from the start.

The right device is the Cyclone V 5CSEMA5F31C6.

Step 26: Select this device:

| New Project Wizard          |                                               |               |                  |                    |                         |                             |

|-----------------------------|-----------------------------------------------|---------------|------------------|--------------------|-------------------------|-----------------------------|

| amily, Device               | & Board Settin                                | ngs           |                  |                    |                         |                             |

| Device Board                |                                               |               |                  |                    |                         |                             |

|                             | d device you want to<br>tional device support | •             |                  | nand on the Too    | ls menu.                |                             |

| To determine the ve         | ersion of the Quartus                         | Prime softwa  | re in which your | target device is   | supported, refer to the | Device Support List webpage |

| Device family               |                                               |               |                  | Show in 'Availa    | ble devices' list       |                             |

| Eamily: Cyclone V           | / (E/GX/GT/SX/SE/ST                           | )             | •                | Pac <u>k</u> age:  | Any                     | •                           |

| Dev <u>i</u> ce: All        |                                               |               | •                | Pin <u>c</u> ount: | Any                     | •                           |

| Target device               | arget device                                  |               |                  |                    | ade: Any                | •                           |

| O <u>A</u> uto device se    | elected by the Fitter                         |               |                  | Name filter:       |                         |                             |

| Specific device             | e selected in 'Available                      | devices' list |                  | Show adva          | nced devices            |                             |

| ○ <u>O</u> ther: n/a        |                                               |               |                  |                    |                         |                             |

| A <u>v</u> ailable devices: |                                               |               |                  |                    |                         |                             |

| Name                        | Core Voltage                                  | ALMs          | Total I/Os       | GPIOs              | GXB Channel PMA         | GXB Channel PCS             |

| 5CSEMA4U23I7                | 1.1V                                          | 15880         | 314              | 314                | 0                       | 0                           |

| 5CSEMA5F31A7                | 1.1V                                          | 32070         | 457              | 457 (              | 0                       | 0                           |

| 5CSEMA5F31C6                | 1.1V                                          | 32070         | 457              | 457 (              | D                       | 0                           |

| 5CSEMA5F31C7                | 1.1V                                          | 32070         | 457              | 457 (              | )                       | 0                           |

Alternatively, you can select the Board tab and select the DE1-SoC board:

| Device           | Board                                |                |                              |                |         |        |            |

|------------------|--------------------------------------|----------------|------------------------------|----------------|---------|--------|------------|

| Select t         | he board/development kit you want to | target for com | npilation.                   |                |         |        |            |

| Family:          | Cyclone V                            |                | <ul> <li>Developn</li> </ul> | nent Kit: Any  |         |        | -          |

| A <u>v</u> ailab | le boards:                           |                |                              |                |         |        |            |

|                  | Name                                 | Version        | Family                       | Device         | Vendor  | ALMs   | Total I/Os |

| -                | Atlas-SoC (DEO-Nano-SoC)             | 1.0            | Cyclone V                    | 5CSEMA4U23C6   | Terasic | 15880  | 314        |

| <b></b>          | Cyclone V E FPGA Development Kit     | 1.0            | Cyclone V                    | 5CEFA7F31I7    | Altera  | 56480  | 480        |

| =                | Cyclone V GT FPGA Development Kit    | 1.0            | Cyclone V                    | 5CGTFD9E5F35C7 | Altera  | 113560 | 616        |

|                  | Cyclone V SoCKit                     | 1.0            | Cyclone V                    | 5CSXFC6D6F31C6 | Arrow   | 41910  | 499        |

|                  | Cyclone V SoC Development Kit        | 1.0            | Cyclone V                    | 5CSXFC6D6F31C6 | Altera  | 41910  | 499        |

|                  | Cyclone V GX Starter Kit             | 1.0            | Cyclone V                    | 5CGXFC5C6F27C7 | Terasic | 29080  | 364        |

| =                | DE0-CV Development Board             | 1.0            | Cyclone V                    | 5CEBA4F23C7    | Terasic | 18480  | 224        |

| =                | DE1-SoC Board                        | 1.0            | Cyclone V                    | 5CSEMA5F31C6   | Altera  | 32070  | 457        |

Step 27: Now click Next until you can Finish the wizard.

We can now see the new project in the "Project Navigator" pane on the left of the Quartus II window. We want to implement "my\_first\_component" on the Cyclone V FPGA that is on the DE1-SoC development and education kit.

You may double-click on "my\_first\_component" on the left side at the tab "Files" to show its source. This can be a schematic, a VHDL file, a Verilog file or anything else that Quartus can handle.

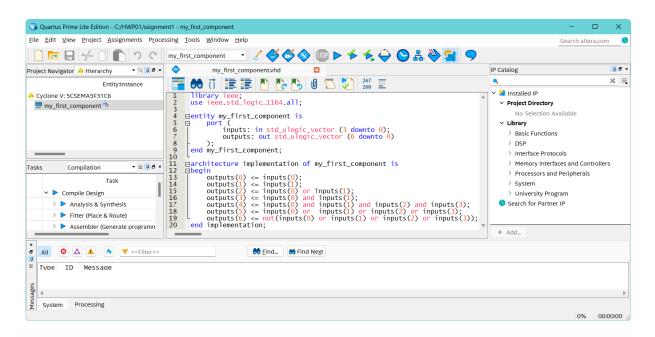

In our case, we know it is our VHDL file we created in ModelSim, so double-clicking it should result in the following:

Because we want ti use VHDL 2008 features in our designs, we have to tell Quartus to use VHDL 2008 as well.

- **Step 28:** Right-click on "my\_first\_component" in the "Project Navigator" pane and select "Settings...".

- **Step 29:** Select Compiler Settings VHDL Input and select VHDL 2008 and click OK:

| Z Settings - my_first_component                                                                                                                                                               | - 0                                                                                                                                                                                                                                                                                            | ×              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Category:                                                                                                                                                                                     | Device/Boar                                                                                                                                                                                                                                                                                    | <sup>.</sup> d |

| General<br>Files<br>Libraries<br>V IP Settings<br>IP Catalog Search Locatior<br>Design Templates<br>V Operating Settings and Cond<br>Voltage<br>Temperature<br>V Compilation Process Settings | VHDL Input         Options for directly compiling or simulating VHDL input files. (Click on the EDA Tool Settings category to enter options for VHDL files generated by other EDA tools.)         VHDL version         VHDL 19 <u>8</u> 7         VHDL 19 <u>9</u> 3         VHDL <u>2</u> 008 |                |

| Incremental Compilation<br><ul> <li>EDA Tool Settings</li> <li>Design Entry/Synthesis</li> <li>Simulation</li> <li>Board-Level</li> <li>Compiler Settings</li> <li>VHDL Input</li> </ul>      | Library Mapping File File name: Show information messages describing LMF mapping during compilation                                                                                                                                                                                            |                |

## 5

## Assigning signals to physical pins

The first thing to do now, is to compile the design in Quartus, to let Quartus know which signals we are using and which signals have to go to the outside world.

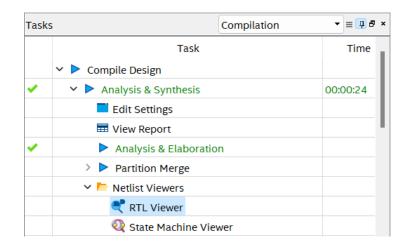

Step 30: In the "Tasks" pane, double-click "Analysis & Synthesis".

If Quartus is done, it will show a green check mark next to the task you performed (if everything went OK). If there are any errors or warnings investigate them and determine if they need to be resolved.

Quartus should show this:

| Quartus Prime Lite Edition - C:/HWP01/ssignm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ent1 - my_first_component                                                                                                                                                                                                                                                                              |                                     |                                                                                                                                                                           | -          | o x        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|

| <u>File Edit View Project Assignments Proc</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | essing <u>T</u> ools <u>W</u> indow <u>H</u> elp                                                                                                                                                                                                                                                       |                                     |                                                                                                                                                                           | Search     | altera.com |

| 🗋 🔂 🚽 🥍 🗋 💼 🤈 ୯                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | my_first_component 🔹 🖌                                                                                                                                                                                                                                                                                 | 🗳 🍑 🗇 🔝 🕨 🗲                         | シ 🌜 🍚 😂 🕹 🙀 🗩                                                                                                                                                             |            |            |

| Project Navigator 🔺 Hierarchy 🔹 🔍 🖪 🖉 🛪                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 🔶 my_first_component.vhd 🛛                                                                                                                                                                                                                                                                             | Compilation Report - my_f           | irst_component 🗵                                                                                                                                                          | IP Catalog | <b>4</b> 5 |

| Entity:Instance         Cyclone V: SCSEMA5F31C6             mmy_first_component           mmy_first_component           mmy_first_component           mmy_first_component           mmy_first_component           mmy_first_component           mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_first_component          mmy_fir | Table of Contents     # #       If How Summary     If Flow Settings       If How Non-Default Global Settin     If How Non-Default Global Settin       If How Clapsed Time     If How Clapsed Time       If How Clapsed Settings     If How Nessages       If How Messages     Flow Suppressed Messages | < <filter>&gt; Flow Status</filter> | Successful - Tue May 23 22:17:43 2023<br>18.1.0 Build 625 09/12/2018 SJ Lite Edit<br>my_first_component<br>Cyclone V<br>SCSEMA5F31C6<br>Final<br>N/A<br>0<br>11<br>0<br>0 |            |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | e resources after synthesis<br>is & Synthesis was success                                                                                                                                                                                                                                              | s - the final resource              |                                                                                                                                                                           | 100        | % 00:00:24 |

In the flow summary, we can see that our design uses 11 pins. The number of pins is correct, since we have 4 inputs and 7 outputs. This means Quartus properly detected which signals we want to connect to the outside world.

We will now assign real world pins of the FPGA to our signals.

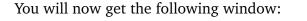

**Step 31:** In the menu, select Assignments Pin Planner.

We see the BGA side of the FPGA chip that we've selected. Our goal is to connect our signals to one of the pins of the chip. We cannot just arbitrarily select some pins because our FPGA resides on a given circuit board. Luckily we have the schematics and a user manual for the board.

We see a list of so-called "nodes" which are actually our signals that have to get a physical connection to the outside world.

Our goal is to connect inputs 0 to 3 to keys 0 to 3 on the DE1-SoC board. Open the user manual<sup>2</sup> and find out at which location those keys are connected.

Do the same for the outputs 0 to 6. We want to connect these to the red LEDs 0 to 6. Once you know all the pin locations for the keys and the LEDs, fill in those locations in the column locations next to their respective nodes. You may just type the pin location instead of searching for it in the dropdown menu.

An example is shown for the first input and output in the list:

<sup>&</sup>lt;sup>2</sup> For boards numbered 1 to 15 the DE1-SoC User Manual revisie C can be find here: https://bitbucket.org/ HR\_ELEKTRO/hwp01/wiki/docs/DE1-SoC\_User\_manual\_revd.pdf. For boards numbered 16 to 50 the DE1-SoC User Manual revisie G can be find here: https://bitbucket.org/HR\_ELEKTRO/hwp01/wiki/docs/DE1-SoC\_User\_manual\_revf.pdf.

| Node Name   | Directior | Location | I/O Bank | VREF Group | I/O Standard    | Reserved | Current Strength | Slew Rate   |

|-------------|-----------|----------|----------|------------|-----------------|----------|------------------|-------------|

| 🖫 inputs[3] | Input     | PIN_Y16  | 3B       | B3B_N0     | 2.5 V (default) |          | 12mA (default)   |             |

| 🖫 inputs[2] | Input     |          |          |            | 2.5 V (default) |          | 12mA (default)   |             |

| 🖫 inputs[1] | Input     |          |          |            | 2.5 V (default) |          | 12mA (default)   |             |

| 🖫 inputs[0] | Input     |          |          |            | 2.5 V (default) |          | 12mA (default)   |             |

| outputs[6]  | Output    | PIN_Y19  | 4A       | B4A_N0     | 2.5 V (default) |          | 12mA (default)   | 1 (default) |

| outputs[5]  | Output    |          |          |            | 2.5 V (default) |          | 12mA (default)   | 1 (default) |

Once you are done connecting all nodes, you may close the pin planner.

## 6

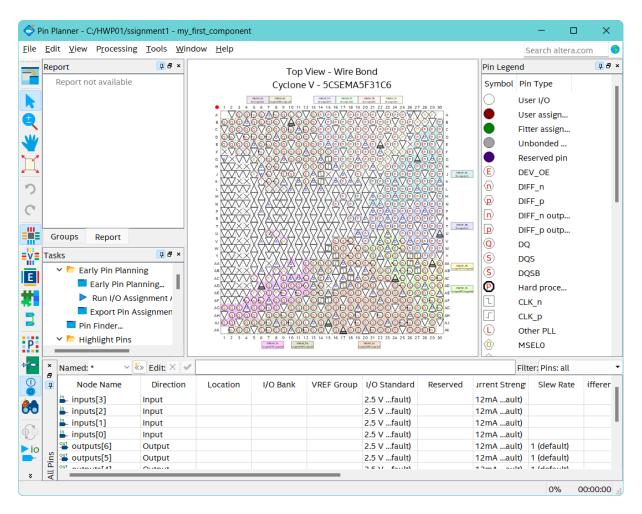

# Place and route the design for FPGA implementation

Now that all nodes are connected to some physical pin, we may let Quartus place and route our new design in the FPGA. This will generate a programming file with which the FPGA will be configured to work as we want.

Step 32: To do this, double-click on the Assembler task:

This step usually takes a relatively long time, compared to compiling a small piece of software, for example. This is another reason why we want to simulate our design before implementing it into the FPGA.

If everything went OK, it should eventually display a pop-up that says the compilation is successful. Ignore any warnings for now.

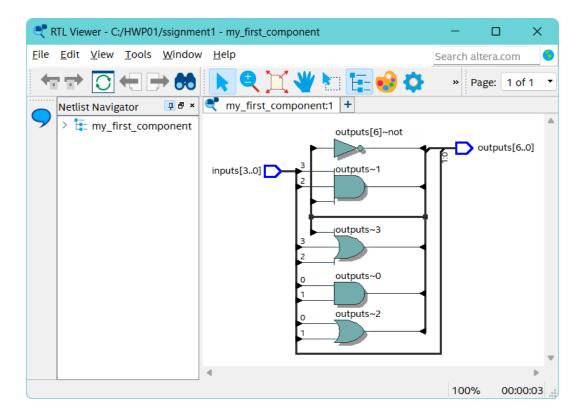

Some interesting things to check is the RTL schematic that Quartus has synthesized from your code.

You may find it here:

The RTL viewer will show the register transfer level schematic of your design.

It should show the following:

Here we may see the logic function that our architecture implements with the given inputs and outputs.

Eventually, writing VHDL code is about thinking how this schematic will look when you write a certain piece of code. (Usually you will think about your schematic in a more macroscopic way, and not as detailed as this.)

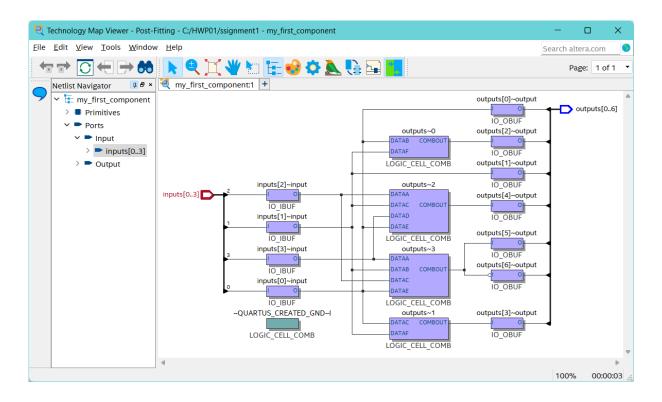

Another interesting view is the "Post-Fitting Technology Map" viewer. Here you can see how the logic elements and other hardware components in the FPGA are used to create your schematic. It can be found here:

| Tasks    | s Compilation                         | ▼≡₽₽×    |

|----------|---------------------------------------|----------|

|          | Task                                  | Time     |

|          | ✓ ► Compile Design                    |          |

| <b>~</b> | > 🕨 Analysis & Synthesis              | 00:00:24 |

| •        | ✓ ► Fitter (Place & Route)            | 00:00:55 |

|          | Edit Settings                         |          |

|          | 🖽 View Report                         |          |

|          | 🛇 Chip Planner                        |          |

|          | 🂐 Technology Map Viewer (Post-Fitting | g)       |

|          | > 🕨 Design Assistant (Post-Fitting)   |          |

We can see the following:

Here we see that it uses just a few logic elements. This is only a tiny fraction of the number of logic elements available (over thirty thousand).

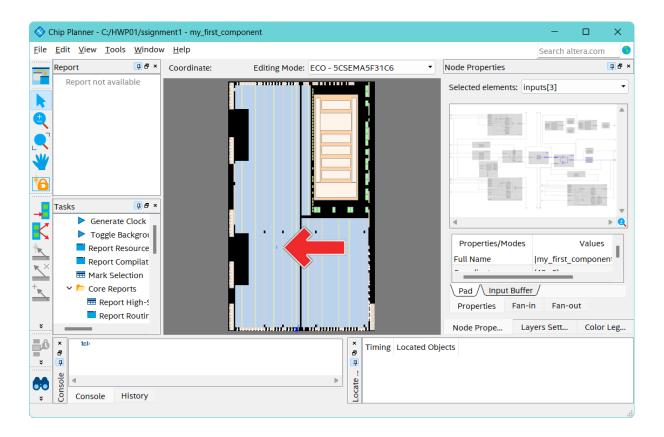

Another interesting thing to look at is the "Chip Planner" which can be found above the "Technology Map Viewer" task.

Here we can see the following:

This is a schematic view of the FPGA chip itself, and it also shows which elements of the chips are used. Only one region is used, and most of the time the unused regions are shut down to save power. The bigger your design is, the more power it will therefore use.

By, the way, the region that is used is not the black region. It is in the middle left, the bit more blueish rectangle, indicated by the red arrow.

| e <u>E</u> dit <u>V</u> iew <u>T</u> ools <u>W</u> indow | <u>H</u> elp         |                                  |                                 | Search altera.com                                                    |

|----------------------------------------------------------|----------------------|----------------------------------|---------------------------------|----------------------------------------------------------------------|

| Report 📮 🗗 🗙                                             | Coordinate: (28, 27) | Editing Mode: ECO - 5CSEMA5F31C6 | <ul> <li>Node Proper</li> </ul> | ties 📮 🗗                                                             |

| Report not available                                     |                      |                                  | Propertie<br>Full Name          | Imy_first_component<br>for art<br>ombinational /<br>s Fan-in Fan-out |

If you zoom in on this, you can see the logic elements that are used:

For specialized and high-speed designs, the tools which you have just seen are extremely useful, because you can manually implement designs in the FPGA if you wish, so to optimize your design. In this course, we will not use them much (except for the RTL viewer).

**Step 33:** On the bottom of the Tasks list, double-click "Program Device". This will open the "Programmer" window:

| Tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Compilation                              | ▼≡∎₽×       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------|