# Hardware Programming HWP01 2022-2023

capturing a FPGA design with VHDL

# **Planning: theory**

- First week

- Introduction digital systems

- Structured digital Design

- RTL

- Third week

- Combinational versus sequential design

- Concurrent and sequential code

• Fourth week

Fifth week

Introduction

machines

machines

to state

Designing

Advanced

state

- Components

- Generics

- Second week

- Introduction VHDL

- Code structure and data types

- Design verification

VHDL design

#### Agenda

- Discussion of previous week

- Signals versus variables

## Signals versus variables

#### • **SIGNAL** properties:

- Can ONLY be declared outside a PROCESS but can be used within a PROCESS

- Within sequential code the signal is not 'updated immediately' (at the end of the PROCESS)

- Only a *single* assignment is allowed to a signal in the whole code (multiple assignments in **PROCESSES** are fine, but only the last one will be effective!)

#### • VARIABLE properties:

- Can ONLY be declared inside a PROCESS

- Is 'updated immediately' and can be used in the next line of code

- Multiple assignments are not a problem

## Agenda

- Discussion of previous week

- Signals versus variables

#### **Putting it together**

HR EAS ELE HWP01 WK1 V1.2

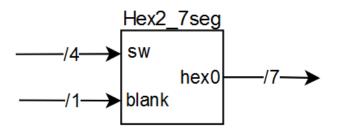

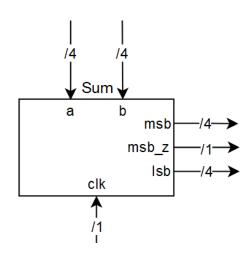

## **Create (separately) validated components**

HR EAS ELE HWP01 WK1 V1.2

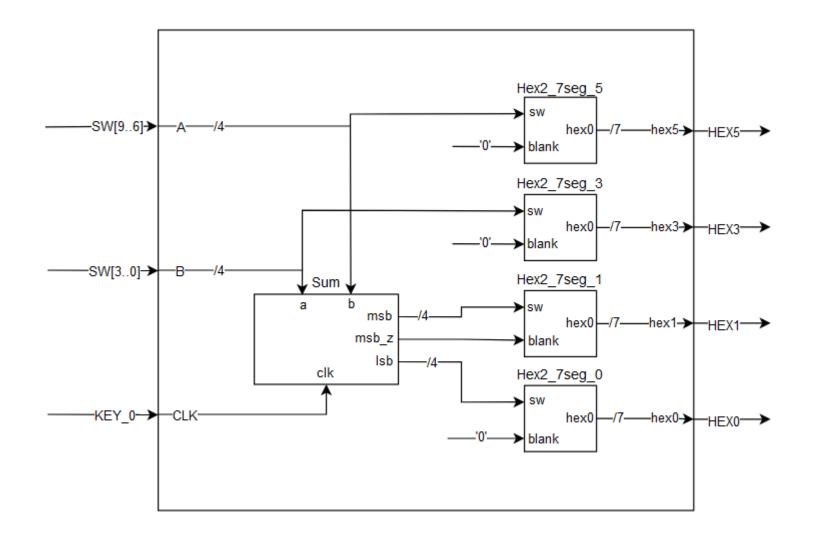

## Add components to your top level design

"Top Level Design: multiply\_2hexandDisplay.vhd"

#### **Instantiating components**

#### begin hex5decoder: seven segment decoder port map( $sw \Rightarrow A$ , $blank \Rightarrow '0'$ , $hex0 \Rightarrow hex5$ ); hex3decoder: seven segment decoder port map( $sw \Rightarrow B$ , $blank \Rightarrow '0'$ , $hex0 \Rightarrow hex3$ ): hexldecoder: seven segment decoder port map( sw => sum msn, blank => blank msn, hex0 => hex1 ); hex0decoder: seven segment decoder port map( $sw \Rightarrow sum lsn, blank \Rightarrow '0', hex0 \Rightarrow hex0$ );

begin

dut: assignment3

```

port map(A => SW(9 downto 6), B => SW(3 downto 0), clk => not KEY(0), hex0 => HEX0, hex1 => HEX1, hex3 => HEX3, hex5 => HEX5);

-- Extra: connect the LEDR outputs to the SW inputs

LEDR <= SW;

end architecture;

```

#### **Generic statements**

- Generic values are used for declaring global constant in a component

- What is the use of generics?

- For more information on generics and what else they are capable of, see CH 6.7

#### **Voorbeeld Generics**

With value

```

entity add_compare_cell is

generic (

NUM_BITS: natural := 16)

port (

a, b: in std_logic_vector(NUM_BITS-1 downto 0);

comp: out std_logic;

sum: out std_logic_vector(NUM_BITS downto 0));

end entity;

```

• Without value

generic (

type bus\_type;

BUS\_WIDTH: natural := 32;

LAST\_ADDRESS: natural);

#### Summary

- Remember the differences between signals and variables

- Components are pre-validated VHDL library elements used to reduce development time of new products.