# Hardware Programming HWP01

capturing a FPGA design with VHDL

## **Fifth Week: Theory**

- Theory:

- Ch15+16: State Machines

- Goals:

- Learn how to design and implement a Finite State

Machine in a digital circuit using VHDL

## Agenda

- Finite State Machines

- Example

- Example in VHDL

- Template in VHDL

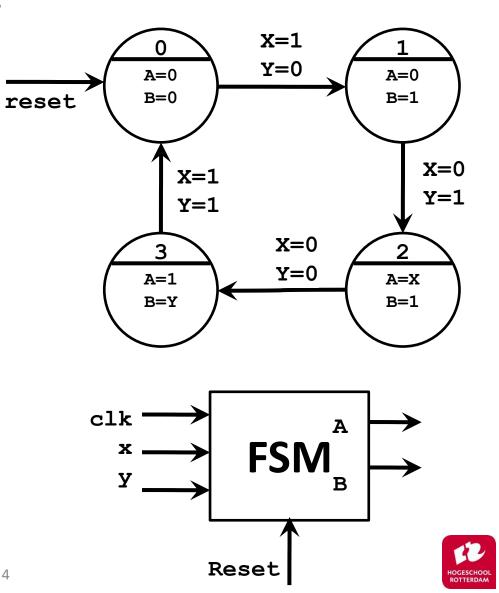

## **Finite State Machines Design**

- FSM diagrams consist of:

- States

- Transitions

- Conditions

- Inputs

- Outputs

- Reset

#### **Finite State Machines in Digital Circuits**

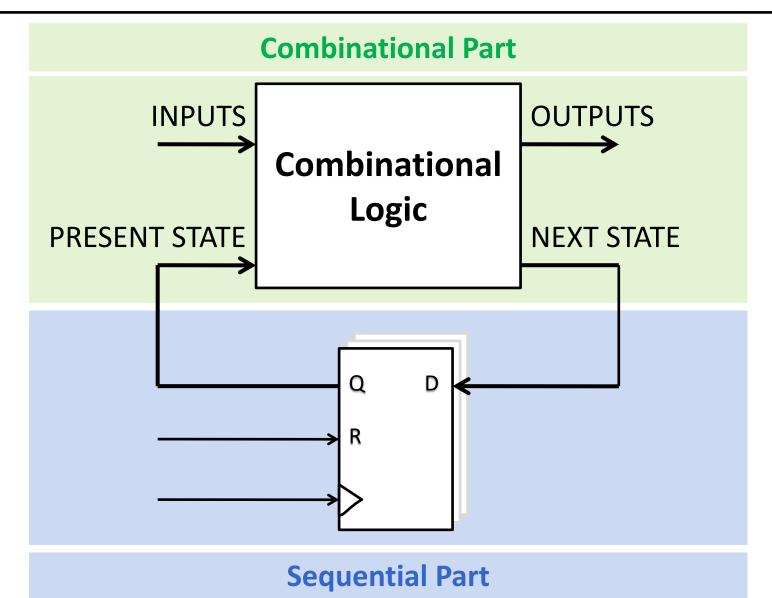

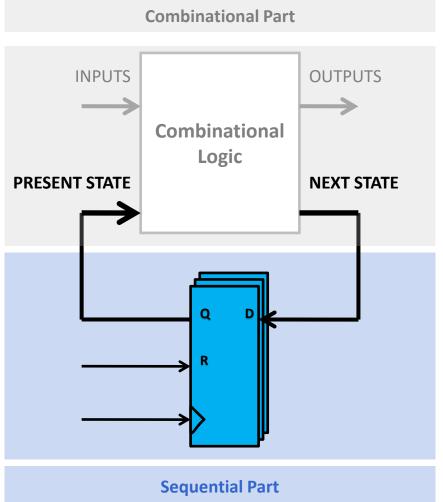

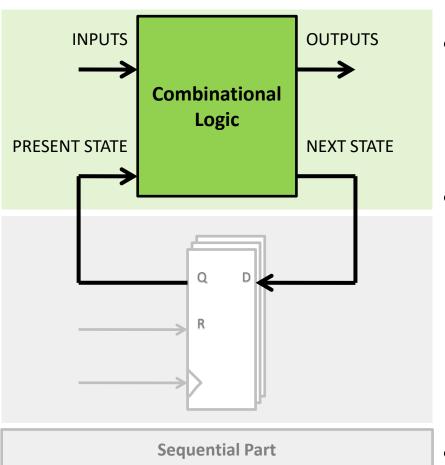

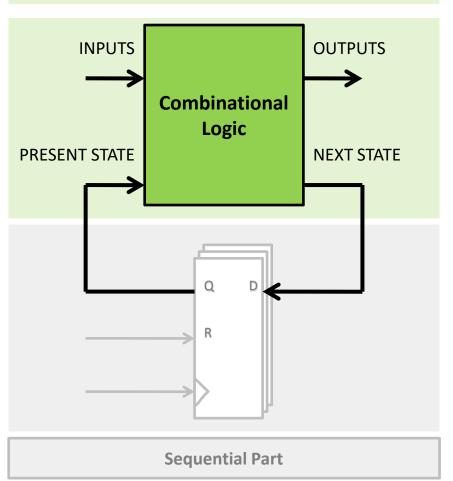

#### **The Sequential Part**

- The sequential part consists only of dffs, a clock and a reset.

- The flip-flops hold the present state

- They switch to the next state on the clock-edge

- The reset makes the present state 0000 (initial state).

- The combinational part determines the next state by the inputs and present state

#### **Encoding the State Bus**

- The states are represented by bits (of course)

- Encoding states can be done in a few ways:

- State BINARY GRAY ONE-HOT

| - 0 | 00 | 00 | 0001 |

|-----|----|----|------|

| - 1 | 01 | 01 | 0010 |

| - 2 | 10 | 11 | 0100 |

| - 3 | 11 | 10 | 1000 |

- Why? (See Ch. 2.6.5)

- Keep it easy, let Quartus decide the encoding.

- See Ch. 15.2 how to do this.

#### **The Combinational Part**

#### **Combinational Part**

Template M1 on page 382

- the combinational part determines the next state

- it is a function of the inputs and present state

- the combinational part determines the outputs

- Moore: it is a function of the present state

- Mealy: it is a function of the present state combined with the inputs

- Always design as Moore and change to Mealy if output needs to react instantly

• <u>Listing</u>

#### **The Combinational Part**

**Combinational Part**

- The Combinational Part is Combinational Logic

- It is a (simple) Boolean Function

- We can draw a truth-table for this

- We can use K-maps to minimize the logic

## Agenda

- Finite State Machines

- Example

- Example in VHDL

- Template in VHDL

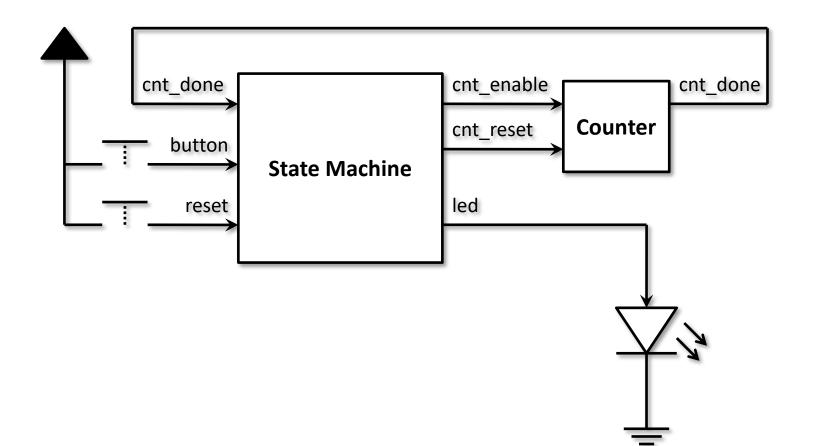

#### **Egg Timer: FSM Context**

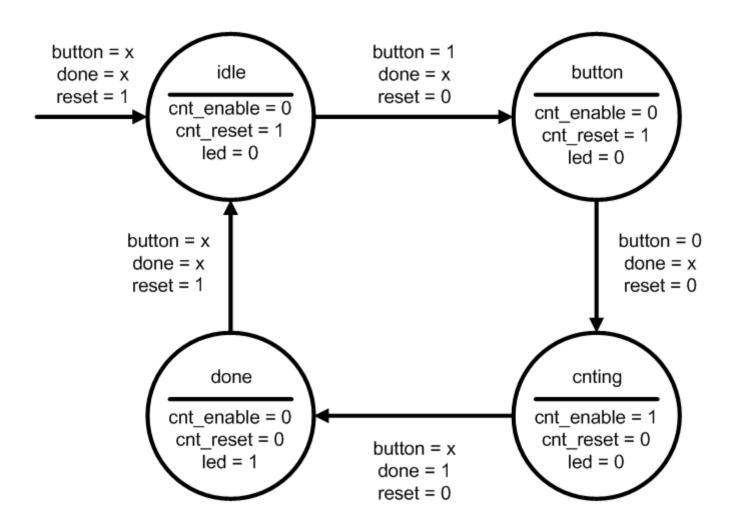

## **Egg Timer: State Diagram**

## Agenda

- Finite State Machines

- Example

- Example in VHDL

- Template in VHDL

## **Example in VHDL**

• Same Egg Timer: the entity

```

library ieee;

use ieee.std_logic_1164.all;

entity fsm_egg_timer is

port(

clk, reset, btn, cnt_done : in std_ulogic;

cnt_enable, cnt_reset, led : out std_ulogic

);

end entity;

```

## **State Bus Encoding in VHDL**

- We need to define the states inside our architecture.

- We can use the "TYPE" keyword, it's like "ENUM" in C. The synthesizer will define what idle, button, cnting, etc... is.

- We need to define signals for the present and next state.

```

architecture rtl of fsm_egg_timer is

-- Define an enumerated type for the state machine

type state_type is (idle, button, cnting, done);

-- Register to hold the current state

signal present_state, next_state : state_type;

begin

```

#### **Define the flip-flops**

#### Write the transitions

```

logic to determine the next state

pr next state : process (present state, btn, cnt done)

begin

case present state is

when idle =>

if btn then

next state <= btn;</pre>

else

next state <= idle;</pre>

end if;

when btn =>

if not btn then

next state <= cnting;</pre>

else

next state <= btn;</pre>

end if;

when cnting =>

if cnt done then

next state <= done;</pre>

else

next state <= cnting;</pre>

end if;

when done =>

next state <= done;</pre>

end case;

end process;

```

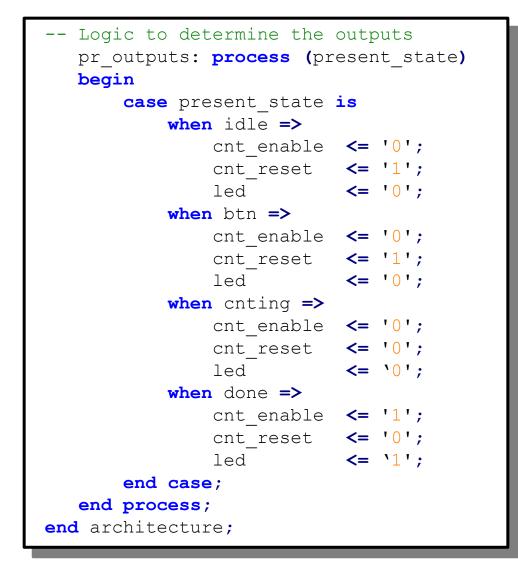

## Write the outputs (Moore)

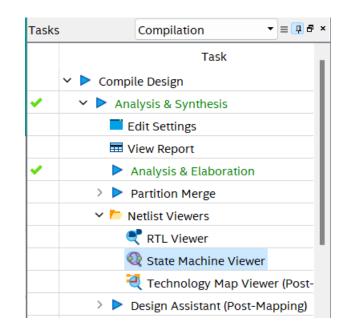

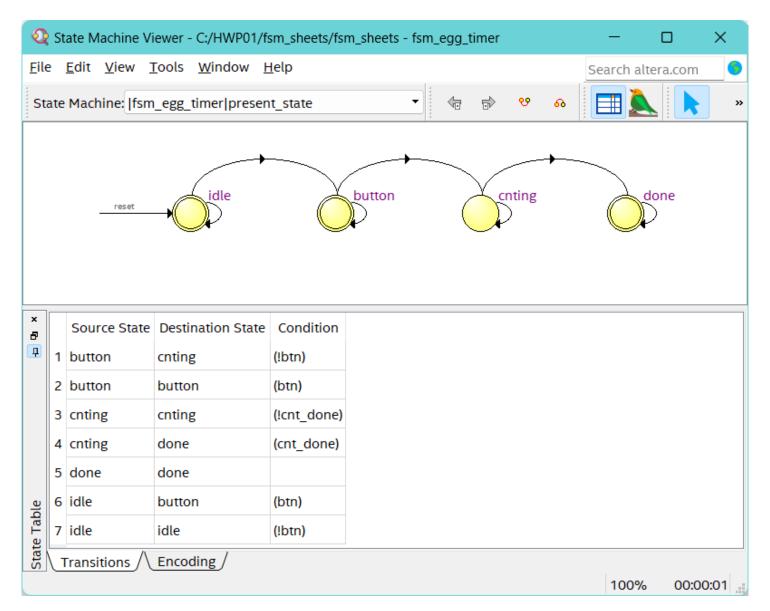

### **State Machine Viewer**

• Quartus can detect a state machine in your code!

## **State Machine Viewer**

## Agenda

- Finite State Machines

- Example

- Example in VHDL

- Template in VHDL

## Write the outputs (Moore)

```

library ieee;

use ieee.std logic 1164.all;

entity fsm is

port (

clk, rst: in std ulogic;

input1, input2, ...: in std ulogic;

output1, output2, ...: out std ulogic

);

end fsm:

architecture behavior of fsm is

type state type is (idle, state1, state2,

...);

signal pr state, nx state: state type;

begin

process(clk, rst)

begin

if rst then

pr state <= idle;</pre>

elsif rising edge(clk) then

pr state <= nx state;</pre>

end if;

end process;

```

• Template M1 on page 382

```

process(pr state, input1, input2, ...)

begin

case pr state is

when idle =>

if input1 then

nx state <= state1;</pre>

else

nx state <= state2;</pre>

end if;

when state1 =>

nx state <= state2;</pre>

when state2 =>

...;

when ... =>

...;

end case;

end process;

process(pr state)

begin

case pr state is

when idle =>

output1 <= '0';</pre>

output2 <= '0';</pre>

. . .

when state1 =>

output1 <= '0';</pre>

output2 <= '1';

. . .

when state2 =>

. . . ;

when ... =>

. . . ;

end case;

end process;

end architecture;

```

ROTTERDAM

• <u>Listing</u>

## Advantages of using the template

- Readability

- Reusability

- Adaptability

- Quicker (especially for bigger designs)

- Quartus also has built-in templates (right-click in the editor)