#### **RTS10 Week 4**

# Planning RTS10

- Week 3: Cooperative Scheduling

- Week 4: Pre-emptive Scheduling

- Week 5: Using an RTOS

- Week 6: Schedulability Analyses, Priority Assignment

- Week 7/8: Introduction (embedded) Rust

#### **Overview**

**REAL-TIME SYSTEMS**

#### Scheduling

- Problem

- Goal

- Possible solution

# Scheduling

**REAL-TIME SYSTEMS**

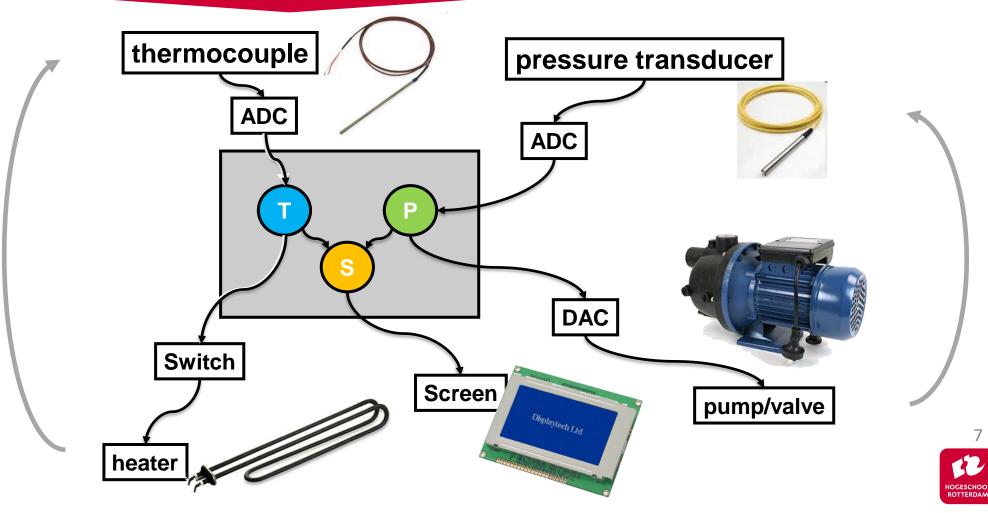

#### Problem

- Multiple processes require CPU time

- Some processes need it asap

- Some processes just need to happen at some point in time

- Multiple processes require bandwidth

- USB, Serial, SPI ....

- Prioritization?

#### Goal

- Create a framework that'll ease (CPU) time management

- Easy to add new processes and to share resources

**REAL-TIME SYSTEMS**

#### Demonstration of pre-emptive project

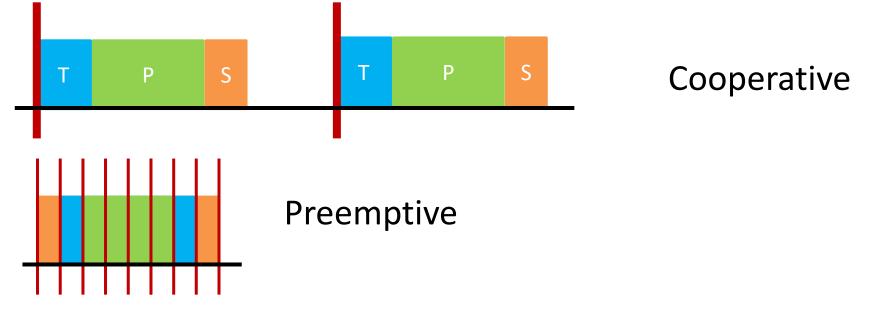

#### **Cooperative versus Pre-emptive scheduling**

REAL-TIME SYSTEMS

#### Cooperative

- Tasks run sequentially

- High priority tasks have to wait till last task finishes

- Easy to set up

- Low overhead scheduler

#### Pre-emptive (Multi-tasking)

- Important tasks always finish first

- Danger of starvation and using hardware concurrently

- More overhead on resources(RAM) and CPU time

#### **Embedded system example**

### **Pre-emption**

**REAL-TIME SYSTEMS**

Interrupting a task to execute a different task

- Scheduler decides next task and can interrupt existing

- Context switch, switches the tasks

#### **Context switch**

#### • What is context?

| 1  | <pre>void * TempControl(void * par)</pre>          | low registers          |

|----|----------------------------------------------------|------------------------|

| 2  | ₽ <mark>{</mark>                                   | low registero          |

| 3  | <pre>int adcSample, dacSample;</pre>               |                        |

| 4  | //P, I, D                                          |                        |

| 5  | <pre>pidSettings pidSetting = {1, 2.3, 0.04}</pre> | }                      |

| 6  | while(1)                                           |                        |

| 7  | e <b>{</b>                                         | high registers <       |

| 8  | <pre>adcRead(&amp;adcSample);</pre>                |                        |

| 9  | <pre>dacSample = pid(100, //setpoint</pre>         | l                      |

| 10 | &pidSetting,                                       |                        |

| 11 | adcToTemp(adcSample)                               |                        |

| 12 | )                                                  | rogram Status Register |

| 13 | <pre>dacWrite(dacSample);</pre>                    |                        |

| 14 | }                                                  |                        |

| 15 | L}                                                 |                        |

**REAL-TIME SYSTEMS**

| ſ            | R0       |

|--------------|----------|

|              | R1       |

|              | R2       |

| ragiatora    | R3       |

| registers {  | R4       |

|              | R5       |

|              | R6       |

| Ļ            | R7       |

| ſ            | R8       |

|              | R9       |

| registers {  | R10      |

|              | R11      |

|              | R12      |

|              | R13 (SP) |

|              | R14 (LR) |

|              | R15 (PC) |

| tus Register | xPSR     |

|              |          |

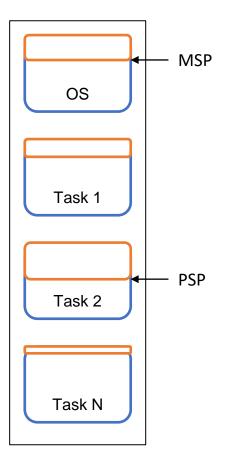

# **OS support in Cortex M4**

- Banked stack pointers

- Privileged and non-privileged operation modes

- Advanced interrupt controller (NVIC)

- Has several interrupts specifically for RT kernels

- Fault handlers

- Memory Protection Unit (MPU)

#### **Banked stack pointers**

| $\left( \right)$        | R0           |  |  |  |  |

|-------------------------|--------------|--|--|--|--|

|                         | R1           |  |  |  |  |

|                         | R2           |  |  |  |  |

| low registers           | R3           |  |  |  |  |

|                         | R4           |  |  |  |  |

|                         | R5           |  |  |  |  |

|                         | R6           |  |  |  |  |

| l                       | R7           |  |  |  |  |

|                         | R8           |  |  |  |  |

|                         | R9           |  |  |  |  |

| high registers          | R10          |  |  |  |  |

|                         | R11          |  |  |  |  |

| l                       | R12          |  |  |  |  |

|                         | R13 (SP)     |  |  |  |  |

|                         | R14 (LR)     |  |  |  |  |

|                         | R15 (PC)     |  |  |  |  |

| Program Status Register | <i>x</i> PSR |  |  |  |  |

- R13 can contain

- the Process Stack Pointer (PSP)

- the Main Stack Pointer (MSP)

- MSP is default

- PSP can be used for separating tasks from the OS

- Normal tasks do not share their stack with the kernel! Much safer.

- Can only be used outside of interrupts

- Set using SPSEL bit in CONTROL register

- Thus far all we have used is the MSP

SP\_process

SP\_main

**REAL-TIME SYSTEMS**

#### Figure 3-3 Processor register set

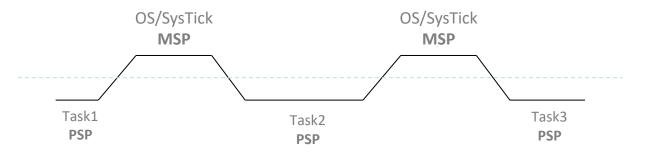

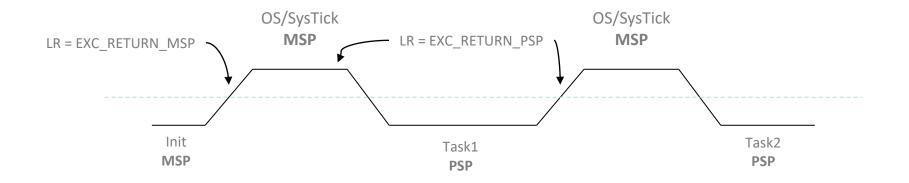

#### Memory usage in a RTOS

- Each task gets own chunk of memory

- The OS uses the MSP

- The tasks use the PSP

- When a new task is selected, the PSP points to the stack of that task.

- Basically, a form of 'Time division multiplexing'

- The scheduling algorithm picks the next task/stack

### **Banked stack pointers**

- Two assembly instructions for accessing special registers

- MRS (move special register value to normal register)

- E.g. MRS R0, PSP ; move PSP value to R0

- MSR (Move normal register value to special register)

- E.g. MSR PSP, R0 ; move R0 value to PSP

- And CMSIS functions

- \_\_get\_PSP(void)

- \_\_set\_PSP(uint32\_t topOfStack)

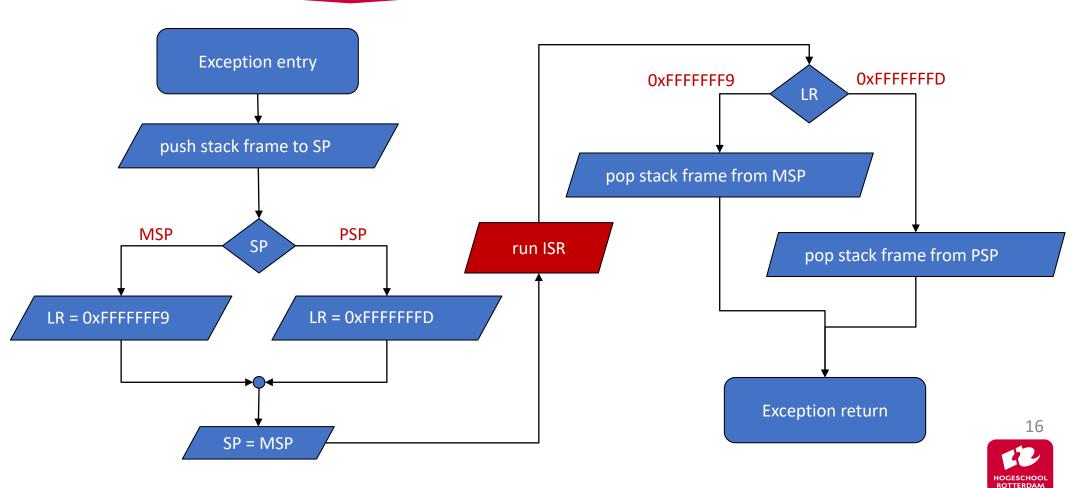

## **Exception entry**

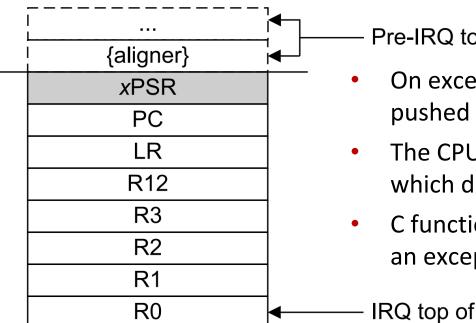

Pre-IRQ top of stack

- On exception several registers are automatically pushed to the current stack pointer

- The CPU writes an EXC\_RETURN value to the LR which determines if the MSP or PSP stack was in use

- C functions are allowed to use RO-R3 and R12 inside an exception.

- IRQ top of stack

Exception frame without floating-point storage

**REAL-TIME SYSTEMS**

Figure 2-3 Exception stack frame

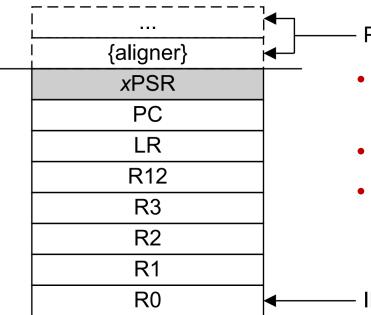

### **Exception return**

Pre-IRQ top of stack

- The CPU checks the EXC\_RETURN value in the LR which determines if the MSP or PSP stack is used

- The CPU pops the stackframe from the MSP or PSP

- The stack used determines the value for the program counter and link register and thus where code execution continues

—— IRQ top of stack

Exception frame without floating-point storage

#### **Exception flowchart**

#### **Example OS**

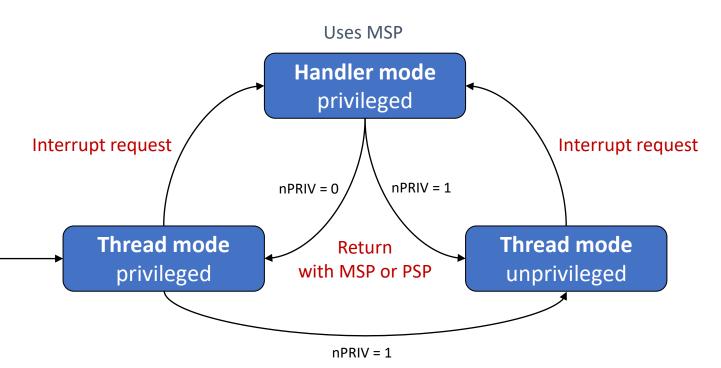

# **Operation modes**

- Security by:

- Separating stacks

- Separating access levels between kernel and tasks.

- nPRIV bit in CONTROL register

- Handler mode

- Used by exceptions

- Privileged Thread mode

- OS intialisation

- OS kernel

- Unprivileged Thread mode

- Used by tasks

- Tasks have limited access to memory

- MPU can be used to change access

ROTTERDAA

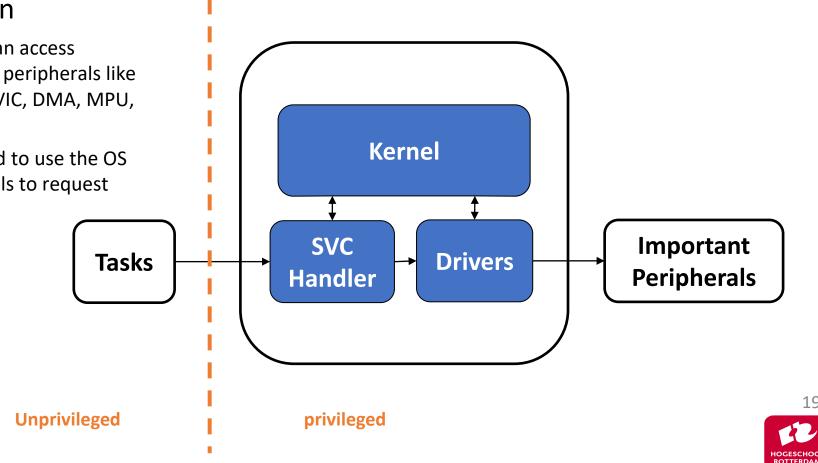

# **Operation modes**

Abstraction

- Only OS can access ٠ important peripherals like Systick, NVIC, DMA, MPU, etc

- Tasks need to use the OS • system calls to request changes

**EMBEDDED SYSTEMS**

19

# **OS Interrupts**

- Systick

- Used by OS to periodically update everything

- PendSV (Pendable Service Call)

- Used by OS to request a context switch

- Software bit triggers this interrupt

- Lowest priority

- SVC (SuperVisor Call)

- Used by tasks to request a service from the OS

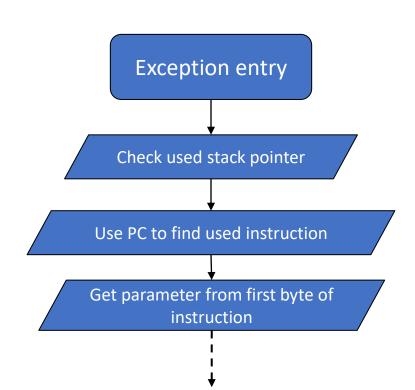

### **Supervisor call**

- Assembly call

- SVC #x

- Parameter X defines which action the OS performs, first byte of instruction

- Interrupt occurs immediately

- You can get and return parameters with stacked registers like normal function call

#### **PendSV - Context switch**

- RO-R3,R12,LR,PC,XPSr get pushed to current stack

- Push {R4-R11} CPU registers to PSP, update stack pointer

- Pick new task and change PSP

- Pop {R4-R11} from new PSP, update stack pointer

- RO-R3,R12,LR,PC,XPSr get popped from current stack

### Switching contaxt

| SWILL                        |                          | ig c                             |          | ιτεχτ                   |       |                                      | 1 v              | oid ta        | ask ()                  |                                                                        |

|------------------------------|--------------------------|----------------------------------|----------|-------------------------|-------|--------------------------------------|------------------|---------------|-------------------------|------------------------------------------------------------------------|

| while (1)                    |                          |                                  | 2 ₽{     |                         |       |                                      |                  |               |                         |                                                                        |

|                              |                          |                                  |          | Enter excep             | ton   | (PendSV)                             | 3                | flo           | oat samp                | les[256];                                                              |

| _                            |                          |                                  |          |                         |       |                                      | 4                |               | -                       | ut[256];                                                               |

| int a,b,c,d,e,f,g;           |                          |                                  | 2.       | Save contex             | t (C  | PU reaister                          | s) to            |               | out outp                | ,uc[200],                                                              |

| Int a,p                      | ,c,a,e,1                 | ,9;                              |          |                         |       |                                      |                  |               |                         |                                                                        |

|                              |                          |                                  |          | stack                   |       |                                      | 6                | while(1)      |                         |                                                                        |

| //perform length calculation |                          |                                  |          |                         |       |                                      | 7 户              | {             |                         |                                                                        |

| a=b* (c+c                    | d/e*f%g)                 | ;                                | 3.       | Switch stack            | (to   | new task                             | 8                |               | pe                      | rformFFT(samples);                                                     |

|                              | -                        |                                  |          |                         |       |                                      |                  | }             |                         |                                                                        |

| //add_t                      | o output                 |                                  | 4.       | Load contex             | t fro | om stack to                          | CPU,             |               |                         |                                                                        |

|                              |                          | queue                            |          |                         |       |                                      |                  |               | 1010                    |                                                                        |

| addToQue                     | eue(a);                  |                                  | 5.       | Leave excep             | tion  | using new                            | (×)= Variables 6 | ថ្លី Expressi | ions didi Regis         | sters 🖾 🤏 Breakpoints                                                  |

| - }                          |                          |                                  | Ē        |                         | -     |                                      |                  |               |                         | 👘 🖧 🕞 💖 📑 🖻 🖉                                                          |

| Name                         | Value                    | Description                      | Ļ        |                         |       | - Pre-IRQ top of s                   | tack             |               | Value                   | Description                                                            |

| ⊿ 👬 Core Registers           |                          |                                  | 1        | {aligner}               | <     |                                      |                  | gisters       |                         |                                                                        |

| 1111 PC                      | 0x00000936               | Program Coun                     |          | xPSR                    |       |                                      | С                | 2             | 0x00000BC6              | Program Counter [Core]                                                 |

| 1111 SP                      | 0x20000640               | General Purpo:                   | _ F      |                         |       |                                      | P                |               | 0x20000204              | General Purpose Register 13 - Stac                                     |

| 1010 LR                      | 0x00000733               | General Purpos                   |          | PC                      |       |                                      | R                |               | 0x00000BD7              | General Purpose Register 14 - Link                                     |

| ⊳ 1000 xPSR                  | 0x21000000               | Stores the state                 |          | LR                      |       |                                      | PS               | R             | 0x61000000              | Stores the status of interrupt enab                                    |

| 888 RO                       | 0x00008000               | General Purpo:                   |          |                         |       |                                      | 0                |               | 0x00000000              | General Purpose Register 0 [Core]                                      |

| 1919 R1                      | 0xE000E100               | General Purpos                   |          | R12                     |       |                                      | 1                |               | 0xFFFFFFFF              | General Purpose Register 1 [Core]                                      |

| 1919 R2                      | 0x200002FC               | General Purpos                   |          | R3                      |       |                                      | 2                |               | 0x0000002               | General Purpose Register 2 [Core]                                      |

| 888 R3                       | 0x00000000<br>0x00000002 | General Purpos<br>General Purpos |          |                         |       |                                      | 3                |               | 0x0000003               | General Purpose Register 3 [Core]                                      |

| 1919 R5                      | 0x00000002               | General Purpo:                   |          | R2                      |       |                                      | 4                |               | 0x0000002<br>0x00000000 | General Purpose Register 4 [Core]                                      |

| 1919 R6                      | 0x00000000               | General Purpo:                   |          | R1                      |       |                                      | 5                |               | 0x00000000              | General Purpose Register 5 [Core]<br>General Purpose Register 6 [Core] |

| 1111 R7                      | 0x20000648               | General Purpo:                   |          |                         |       |                                      | 7                |               | 0x20000648              | General Purpose Register 7 [Core]                                      |

| 1111 R8                      | 0x00000000               | General Purpos                   |          | R0                      | ◀     | <ul> <li>IRQ top of stack</li> </ul> | , 8              |               | 0x00000000              | General Purpose Register 8 [Core]                                      |

| 888 R9                       | 0x00000000               | General Purpo:                   |          |                         |       |                                      | 9                |               | 0x00000000              | General Purpose Register 9 [Core]                                      |

| 1889 R10                     | 0xA4420001               | General Purpos                   | F        | Exception frame without | ł     |                                      | 10               |               | 0xA4420001              | General Purpose Register 10 [Core]                                     |

| 1010 R11                     | 0x400FD108               | General Purpos                   |          |                         | •     |                                      | 11               |               | 0x400FD108              | General Purpose Register 11 [Core]                                     |

| 888 R12                      | 0x400FD000               | General Purpos                   | Π        | oating-point storage    |       |                                      | 12               |               | 0x000000C               | General Purpose Register 12 [Core]                                     |

| 888 R13                      | 0x20000640               | General Purpose                  | Register | 13 [Core]               |       |                                      | 1889 R13         |               | 0x20000204              | General Purpose Register 13 [Core]                                     |

| 1919 R14                     | 0x00000733               | General Purpose                  | Register | 14 [Core] 👻             |       |                                      | 1919 R14         |               | 0x00000BD7              | General Purpose Register 14 [Core]                                     |

### **Memory Protection Unit**

**REAL-TIME SYSTEMS**

- Can set memory locations

- Inaccessible

- Read only

- Non-executable

- Possible use-case in RTOS

- Limit access to certain peripherals

- Only allow access to own task memory (and thus stack)

- Downside?

- Make RAM segments non-executable to prevent injection-type attacks

FreeRTOS-MPU - ARM Cortex-M3 and ARM Cortex-M4 Memory Protection Unit support in FreeRTOS

REAL-TIME SYSTEMS

#### Priority based

- Scheduler decides and update states of tasks

- When high priority task comes alive, it interrupts lower priority tasks

- When all tasks are suspended, the idle task can run

Round robin

- Every task gets equal CPU time

- When all tasks are suspended, the idle task can run

#### Demo

• Instructor demonstrates algorithms

## **Problems with pre-emptive scheduling**

**REAL-TIME SYSTEMS**

#### Starvation

- Low priority tasks don't get cpu time

- Possible solution: Aging

#### Sharing resources

- Tasks can't use hardware 'simultaneously'

- Waiting for hardware to come available can cause deadlock or priority inversion

- Next week

# Walkthrough VersdOS

#### **Next Week**

**REAL-TIME SYSTEMS**

#### Free-RTOS

- What is it

- Problems and challenges with

- Threads and IPC (Inter Process Synchronization)

- POSIX API overview

Read assignment 5 before next week's lesson!

### Aan de slag!